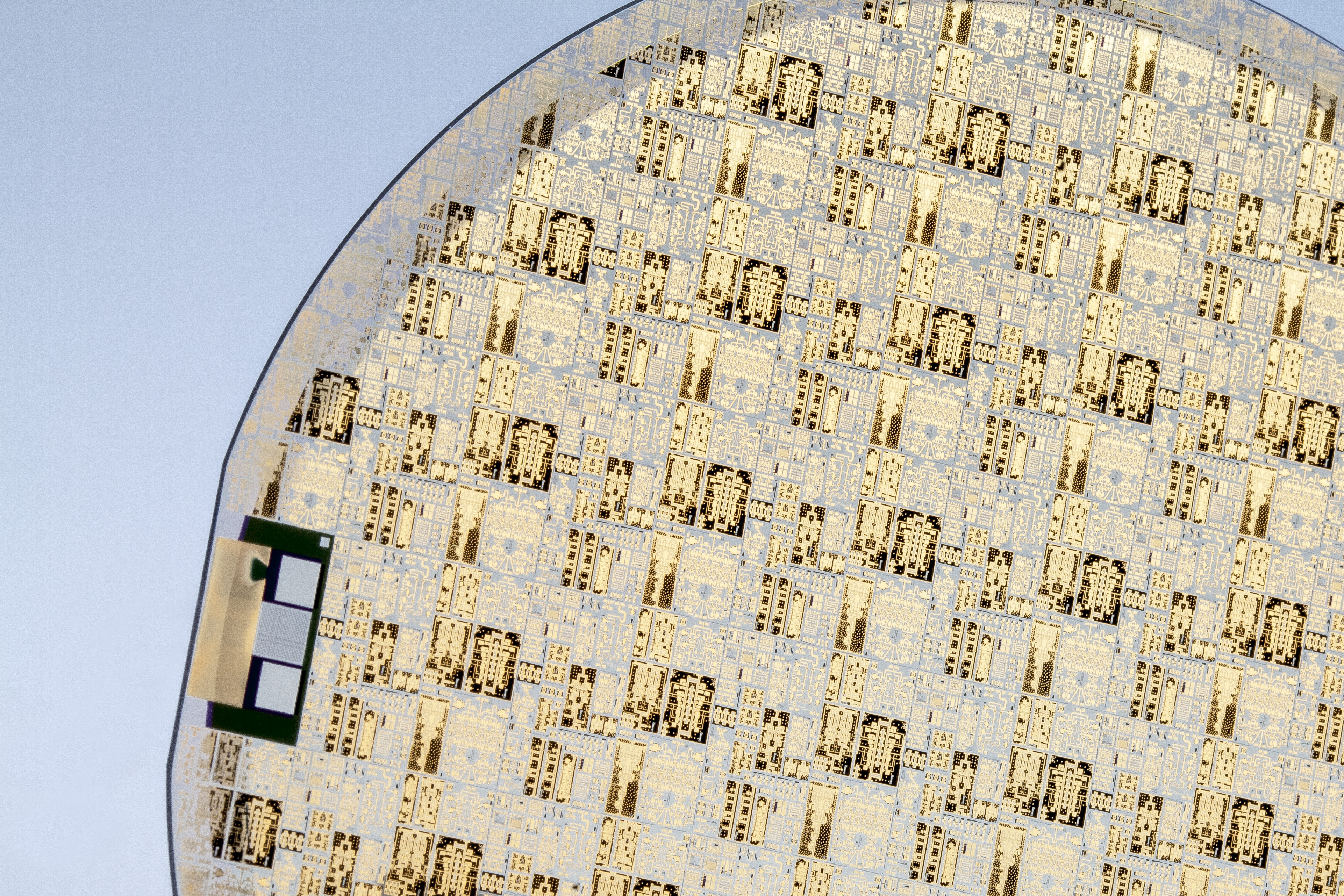

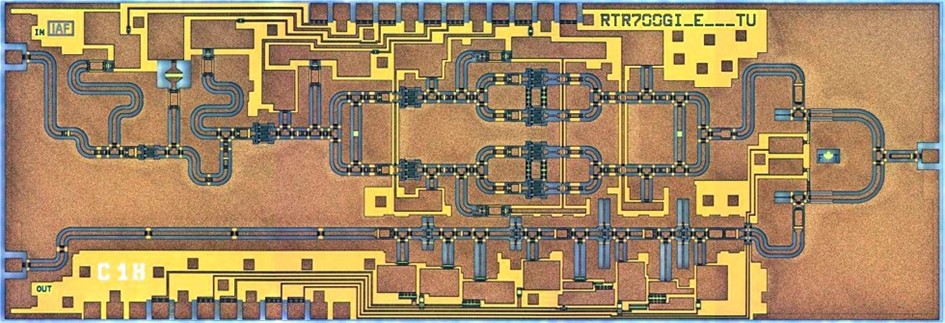

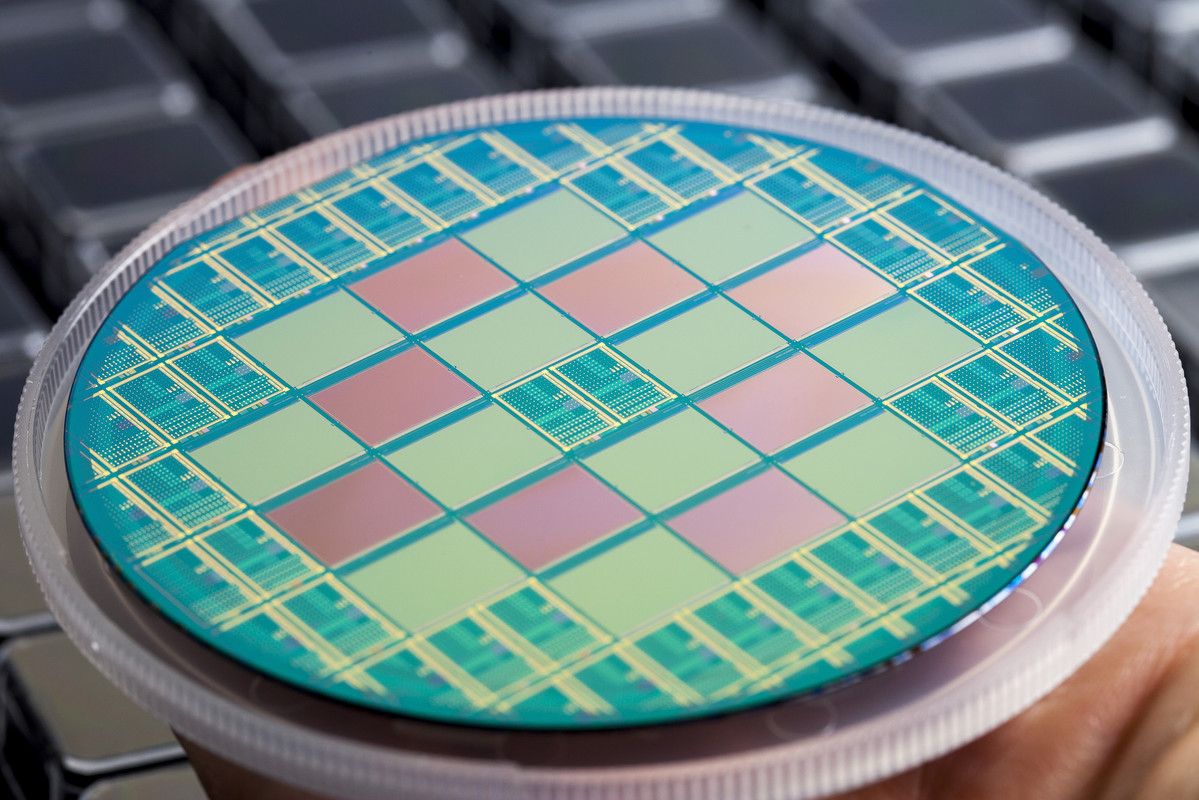

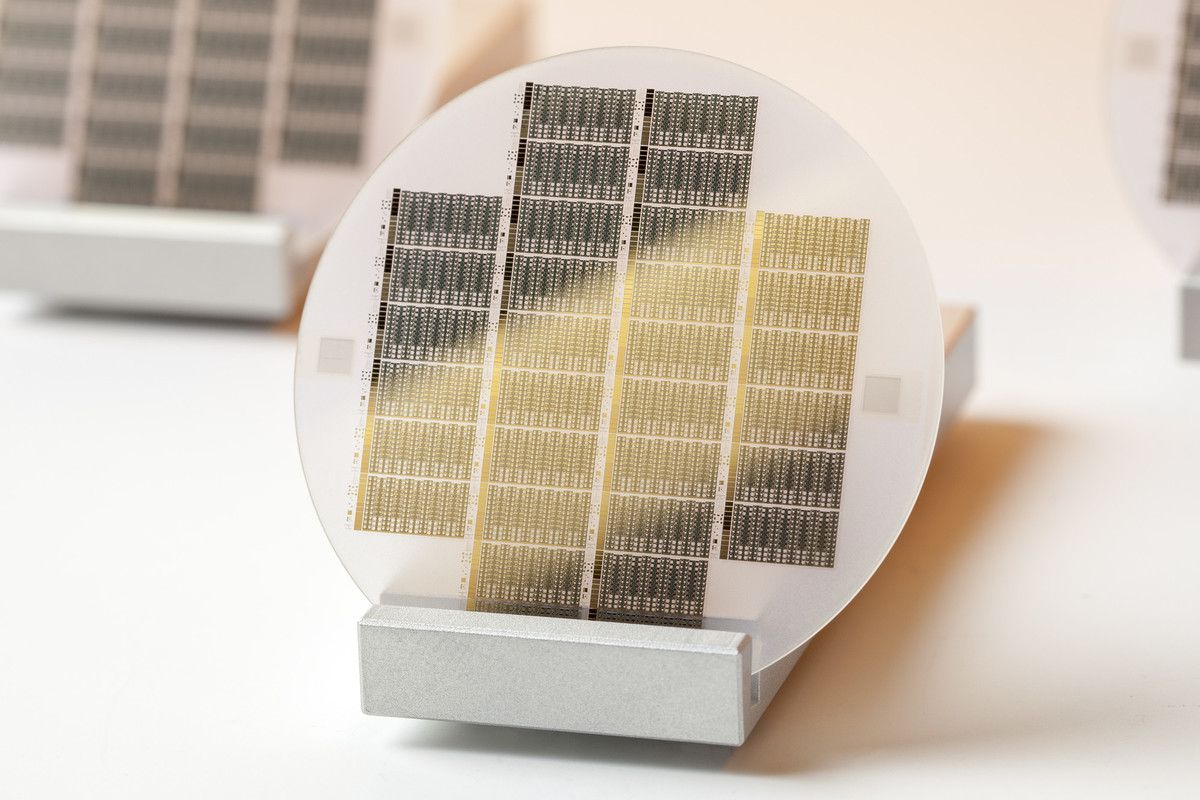

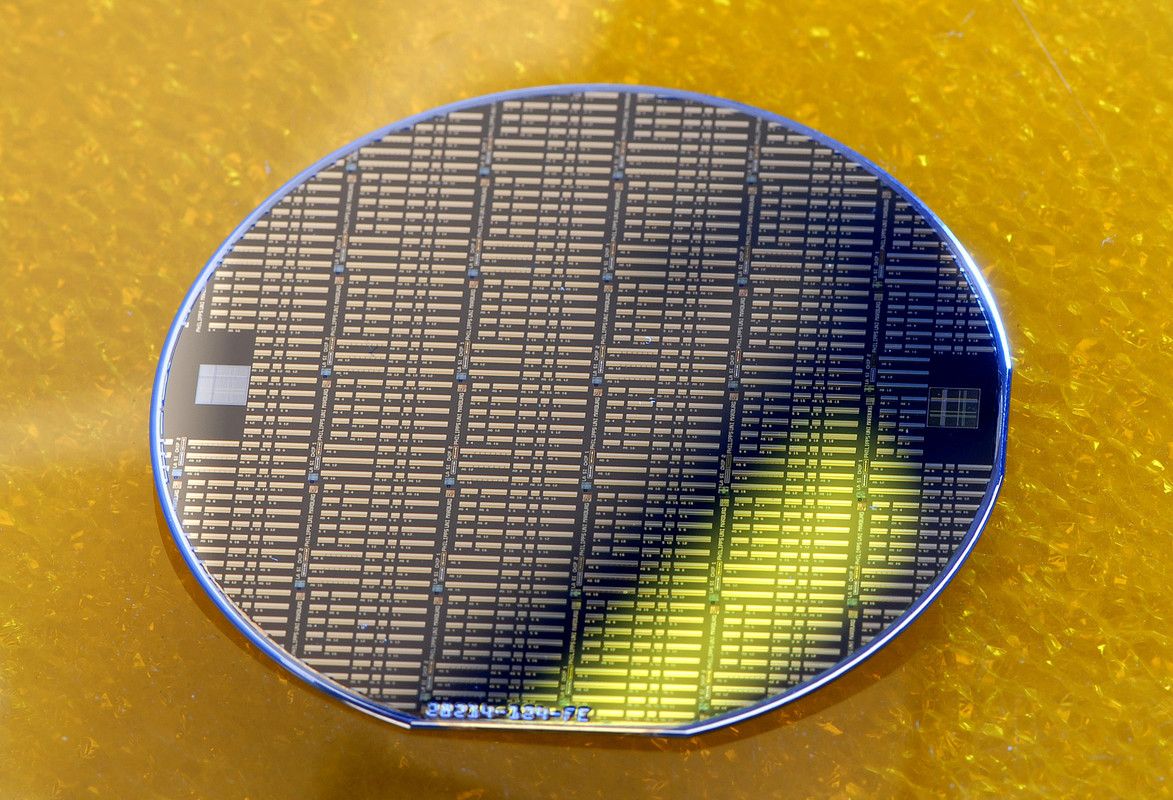

Wafer Runs for transistors, integrated circuits (ICs) as well as electronic and optoelectronic devices

Based on its epitaxial and technological capabilities, Fraunhofer IAF offers (multi-project) wafer runs (MPW), entire mask processing and the realization of electronic and optoelectronic devices for external customers. Both frontside and backside processing is possible. The runs are offered regularly every four to six months.

Fraunhofer IAF has a state-of-the-art clean room for processing of cutting-edge III-V semiconductor devices with e-beam, optical stepper, and laser lithography as well as deposition and etching of various dielectrics and metals. In order to maintain and expand its excellent processing capabilities, Fraunhofer IAF invests in new equipment every year.

Fraunhofer Institute for Applied Solid State Physics IAF

Fraunhofer Institute for Applied Solid State Physics IAF